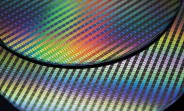

TSMC announced its ground-breaking 1.6nm manufacturing process for chips and it also includes backside power delivery network that improves power efficiency and transistor density even further.

The announced 1.6nm process relies on gate-all-around nanosheet transistors, just like the upcoming N2, N2P and N2X architectures based on the 2nm node. The new process alone allows 10% higher clock speeds at the same voltage and up to 20% lower power drain at the same frequency and complexity. Depending on the chip design, the new 1.6nm process can also fit up to 10% more…

TSMC announced its ground-breaking 1.6nm manufacturing process for chips and it also includes backside power delivery network that improves power efficiency and transistor density even further.

The announced 1.6nm process relies on gate-all-around nanosheet transistors, just like the upcoming N2, N2P and N2X architectures based on the 2nm node. The new process alone allows 10% higher clock speeds at the same voltage and up to 20% lower power drain at the same frequency and complexity. Depending on the chip design, the new 1.6nm process can also fit up to 10% more… Read More GSMArena.com – Latest articles

+ There are no comments

Add yours